Техпроцесс TSMC N5P обеспечивает повышение плотности размещения транзисторов на 84-87%

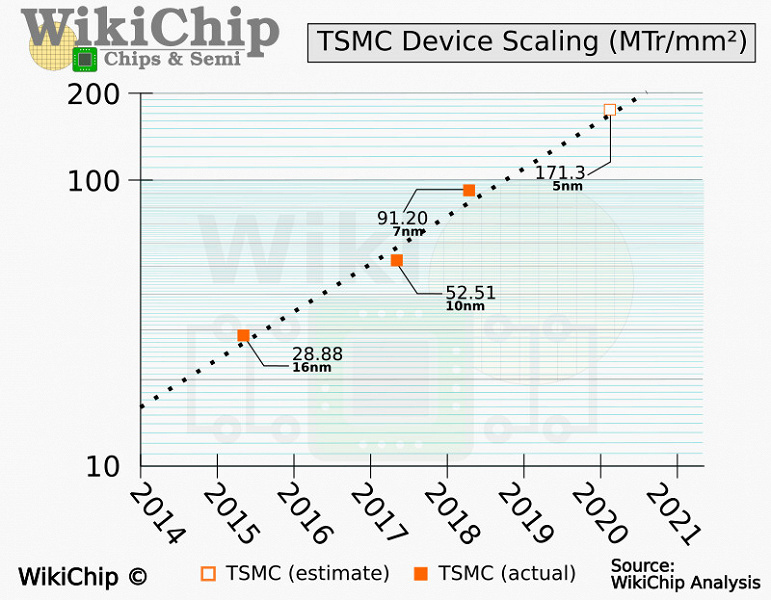

Проанализировав 5-нанометровый техпроцесс TSMC N5P, специалисты WikiChip признали значительное повышение плотности размещения транзисторов на кристалле по сравнению с N7 — наиболее передовым на сегодня техпроцессом TSMC, в котором не используется EUV. Как утверждается, выигрыш достигает 87%. Отметим, что собственная оценка TSMC составляет 84%. Ожидается, что выпуск продукции с применением техпроцесса N5P начнется в конце этого года. Рисковое производство по предшествующему техпроцессу TSMC N5 уже началось в начале года, а коммерческое должно начаться в апреле или мае, если сроки не будут сорваны пандемией COVID-19.

СМОТРИ ТАКЖЕ

- Компания Samsung вытеснила Apple из первой тройки производителей процессоров для смартфонов

- Начались продажи устройства HyperX ChargePlay Clutch for Mobile

- В Германии появился онлайновый калькулятор, позволяющий оценить запасы туалетной бумаги

- Xiaomi прекращает работы над MIUI 11

- Huami — уже №3 в России, Xiaomi Mi Band 5 выйдет только в конце 2020 года

- Snapdragon 720G и квадрокамера за $180: стартовали продажи Redmi Note 9S

- Wingtech, Huaqin и Longcheer. С большой вероятностью ваш смартфон разработан специалистами одной из этих компаний

- В прошлом году панелей OLED было продано на 28 млрд долларов

- Утечка указывает на скорый анонс объектива HD Pentax-D FA * 85mm f/1.4 SDM AW

- Кения одобрила полеты стратостатов Loon